Product Summary

The 74HC574N is a high-speed Si-gate CMOS device and is pin compatible with low power Schottky TTL (LSTTL). The 74HC574N is specified in compliance with JEDEC standard no. 7A. The 74HC574N is octal D-type flip-flops featuring separate D-type inputs for each flip-flop and non-inverting 3-state outputs for bus oriented applications. A clock (CP) and an output enable (OE) input are common to all flip-flops.

Parametrics

74HC574N absolute maximum ratings: (1)tPHL/ tPLH propagation delay CP to Qn CL = 15 pF; VCC=5V: 14ns for HC, 15ns for HCT; (2)fmax maximum clock frequency: 123MHz for HC, 76 MHz for HCT; (3)CI input capacitance: 3.5pF; (4)CPD power dissipation capacitance per flip-flop: 22pF for HC, 25pF for HCT; (5)tsu set-up time Dn to CP: 12 ns; (6)th hold time Dn to CP: 5 ns; (7)fmax maximum clock pulse frequency: 30MHz.

Features

74HC574N features: (1)3-state non-inverting outputs for bus oriented applications; (2)8-bit positive edge-triggered register; (3)Common 3-state output enable input; (4)Independent register and 3-state buffer operation; (5)Output capability: bus driver; (6)ICC category: MSI.

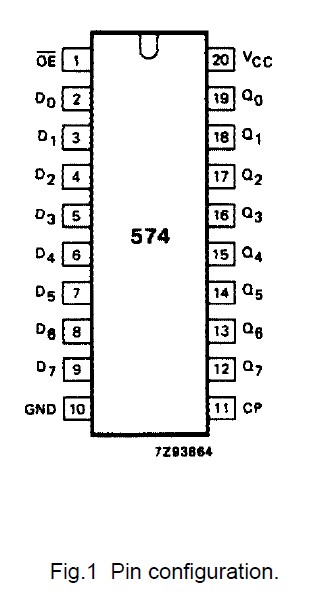

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

74HC574N |

NXP Semiconductors |

Flip Flops OCTAL D F/F POS-EDGE 3STATE |

Data Sheet |

Negotiable |

|

||||||||||||

|

74HC574N,652 |

NXP Semiconductors |

Flip Flops OCTAL D F/F POS-EDGE |

Data Sheet |

|

|

||||||||||||

(Hong Kong)

(Hong Kong)