Product Summary

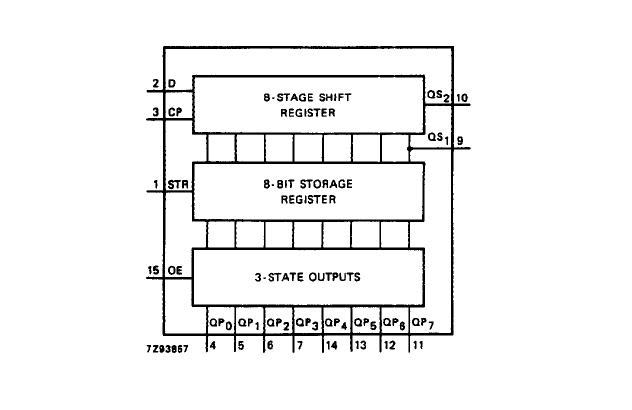

The 74HC4094N is a high-speed Si-gate CMOS device and is pin compatible with the “4094” of the “4000B” series. It is specified in compliance with JEDEC standard no. 7A. The 74HC4094N is 8-stage serial shift registers having a storage latch associated with each stage for strobing data from the serial input (D) to the parallel buffered 3-state outputs (QP0 to QP7). The parallel outputs may be connected directly to common bus lines. Data is shifted on the positive-going clock (CP) transitions. The applications of the 74HC4094N include Serial-to-parallel data conversion, Remote control holding register.

Parametrics

74HC4094N absolute maximum ratings: (1) propagation delay (CL = 15pF; VCC = 5V): 15ns for HC, 19ns for HCT; (2) maximum clock frequency: 95MHz for HC, 86MHz for HCT; (3) input capacitance: 3.5pF; (4)power dissipation capacitance per package: 83pF for HC, 92pF for HCT.

Features

74HC4094N features: (1) Output capability: standard; (2) ICC category: MSI.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

74HC4094N,652 |

NXP Semiconductors |

Counter Shift Registers 8-STAGE BUS REGISTER |

Data Sheet |

|

|

||||||||||||

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||

|

74HC |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||

|

74HC/HCT02 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||

|

74HC/HCT03 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||

|

74HC/HCT10 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||

|

74HC/HCT107 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||

|

74HC/HCT109 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||

(Hong Kong)

(Hong Kong)