Product Summary

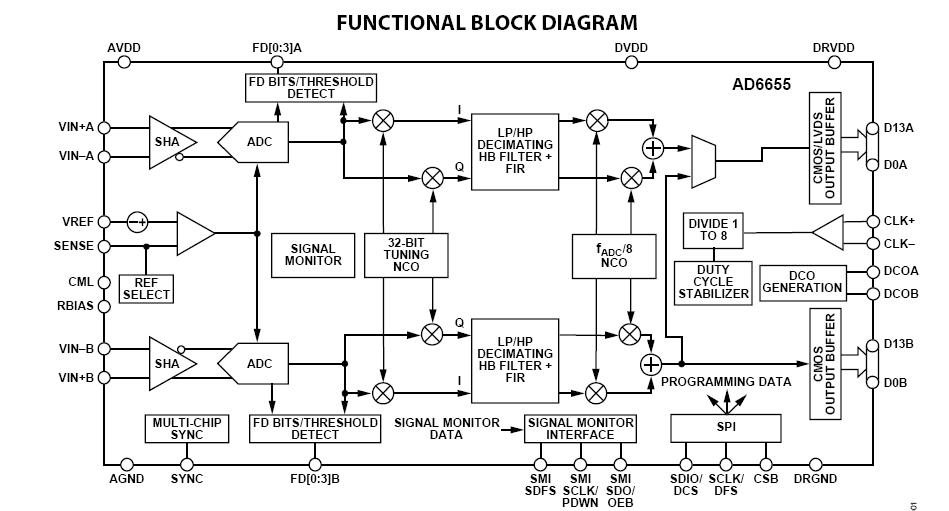

The AD6655ABCPZ-125 is an IF Diversity Receiver consisting of dual 14-bit, 80 MSPS/105 MSPS/125 MSPS/150 MSPS ADCs and a wideband digital down converter (DDC). The AD6655ABCPZ-125 is designed to support communications applications where low cost, small size and versatility are desired. The applications of the AD6655ABCPZ-125 include Communications, Diversity radio systems, Multimode digital receivers (3G), TD-SCDMA, WiMax, WCDMA, CDMA2000, GSM, EDGE, LTE, I/Q demodulation systems, Smart antenna systems, General-purpose software radios, Broadband data applications.

Parametrics

AD6655ABCPZ-125 absolute maximum ratings: (1)AVDD, DVDD to AGND: -0.3 V to +2.0 V; (2)DRVDD to DRGND: -0.3 V to +3.9 V; (3)AGND to DRGND: -0.3 V to +0.3 V; (4)VIN+A/VIN+B, VIN-A/VIN.B to AGND: -0.3 V to AVDD + 0.2 V; (5)CLK+, CLK. to AGND: -0.3 V to +3.9 V; (6)SYNC to AGND: -0.3 V to +3.9 V; (7)VREF to AGND: -0.3 V to AVDD + 0.2 V; (8)SENSE to AGND: -0.3 V to AVDD + 0.2 V; (9)CML to AGND: -0.3 V to AVDD + 0.2 V; (10)RBIAS to AGND: -0.3 V to AVDD + 0.2 V; (11)CSB to AGND: -0.3 V to +3.9 V; (12)SCLK/DFS to DRGND: -0.3 V to +3.9 V; (13)SDIO/DCS to DRGND: -0.3 V to DRVDD + 0.3 V; (14)SMI SDO/OEB to DRGND: -0.3 V to DRVDD + 0.3 V; (15)SMI SCLK/PDWN to DRGND: -0.3 V to DRVDD + 0.3 V; (16)SMI SDFS to DRGND: -0.3 V to DRVDD + 0.3 V; (17)D0A/D0B through D13A/D13B to DRGND: -0.3 V to DRVDD + 0.3 V; (18)FD0A/FD0B through FD3A/FD3B to DRGND: -0.3 V to DRVDD + 0.3 V; (19)DCOA/DCOB to DRGND: -0.3 V to DRVDD + 0.3 V; (20)Operating Temperature Range (Ambient): -40℃ to +85℃; (21)Maximum Junction Temperature Under Bias: 150℃; (22)Storage Temperature Range (Ambient): -65℃ to +125℃.

Features

AD6655ABCPZ-125 features: (1)SNR = 74.5 dBc (75.5 dBFS) in a 32.7 MHz BW at 70 MHz @ 150 MSPS; (2)SFDR = 80 dBc to 70 MHz @ 150 MSPS; (3)1.8 V analog supply operation; (4)1.8 V to 3.3 V CMOS output supply or 1.8 V LVDS output supply; (5)Integer 1-to-8 input clock divider; (6)Integrated dual-channel ADC; (7)Sample rates up to 150 MSPS; (8)IF sampling frequencies to 450 MHz; (9)Internal ADC voltage reference; (10)Integrated ADC sample-and-hold inputs; (11)Flexible analog input range: 1 V p-p to 2 V p-p; (12)ADC clock duty cycle stabilizer; (13)95 dB channel isolation/crosstalk; (14)Integrated wideband digital down converter (DDC); (15)32-bit complex, numerically controlled oscillator (NCO); (16)Decimating half-band filter and FIR filter; (17)Supports real and complex output modes; (18)Fast attack/threshold detect bits; (19)Composite signal monitor; (20)Energy-saving power-down modes.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

AD6655ABCPZ-125 |

|

IC IF RCVR 14BIT 125MSPS 64LFCSP |

Data Sheet |

|

|

||||||||||

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||

|

AD660 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||

|

AD6600 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||

|

AD6600AST |

Analog Devices Inc |

IC ADC DUAL W/RSSI 44-LQFP |

Data Sheet |

Negotiable |

|

||||||||||

|

AD6600AST-REEL |

Analog Devices Inc |

IC ADC DUAL W/RSSI 44-LQFP T/R |

Data Sheet |

Negotiable |

|

||||||||||

|

AD6600ASTZ |

|

IC ADC DUAL W/RSSI 44-LQFP |

Data Sheet |

|

|

||||||||||

|

AD6600ASTZ-REEL |

|

IC ADC DUAL W/RSSI 44-LQFP T/R |

Data Sheet |

|

|

||||||||||

(Hong Kong)

(Hong Kong)