Product Summary

The 74HC273N is a high-speed Si-gate CMOS device. It is pin compatible with low power Schottky TTL(LSTTL). The device is specified in compliance with JEDEC standard no.7A. The 74HC273N has eight edge-triggered, D-type flip-flops with individual D inputs and Q outputs. The common clock (CP) and master reset (MR) inputs load and reset (clear) all flip-flops simultaneously. The 74HC273N is useful for applications where the true output only is required and the clock and master reset are common to all storage elements.

Parametrics

74HC273N quick reference data:(1)propagation delay(CL = 15pF; VCC =5 V):CP to Qn:15ns,MR to Qn:15ns; (2)maximum clock frequency:66MHz; (3)input capacitance:3.5pF; (4)power dissipation capacitance per flip-flop:20pF.

Features

74HC273N features: (1)Ideal buffer for MOS microprocessor or memory; (2)Common clock and master reset; (3)Eight positive edge-triggered D-type flip-flops; (4)See “377” for clock enable version; (5)See “373” for transparent latch version; (6)See “374” for 3-state version; (7)Output capability; standard; (8)ICC category: MSI.

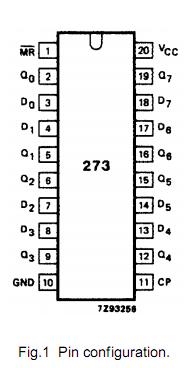

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

74HC273N,652 |

NXP Semiconductors |

Flip Flops OCTAL D F/F W/RESET |

Data Sheet |

|

|

||||||||||||

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||

|

74HC |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||

|

74HC/HCT02 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||

|

74HC/HCT03 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||

|

74HC/HCT10 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||

|

74HC/HCT107 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||

|

74HC/HCT109 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||

(Hong Kong)

(Hong Kong)