Product Summary

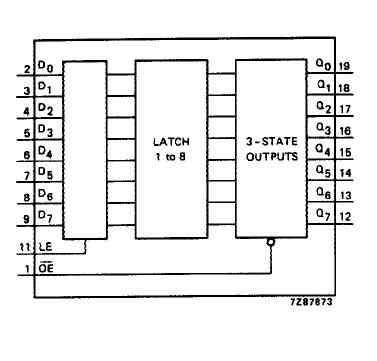

The 74HC573PWR is a high-speed Si-gate CMOS device and are pin compatible with low power Schottky TTL (LSTTL). The 74HC573PWR is specified in compliance with JEDEC standard no. 7A. The 74HC573PWR is a octal D-type transparent latch featuring separate D-type inputs for each latch and 3-state outputs for bus oriented applications.

Parametrics

74HC573PWR absolute maximum ratings: (1) propagation delay nA to nY (CL = 15pF; VCC = 5V): 14ns for HC, 17ns for HCT; (2) input capacitance: 3.5pF; (3) power dissipation capacitance per gate: 26pF for HC, 26pF for HCT.

Features

74HC573PWR features: (1)Inputs and outputs on opposite sides of package allowing easy interface with microprocessors; (2)Useful as input or output port for microprocessors/microcomputers; (3)3-state non-inverting outputs for bus oriented applications; (4)Common 3-state output enable input; (5)Functionally identical to the “563” and “373”; (6)Output capability: bus driver; (7)ICC category: MSI.

Diagrams

|

74HC |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

74HC/HCT02 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

74HC/HCT03 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

74HC/HCT10 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

74HC/HCT107 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

74HC/HCT109 |

Other |

|

Data Sheet |

Negotiable |

|

||||

(Hong Kong)

(Hong Kong)