Product Summary

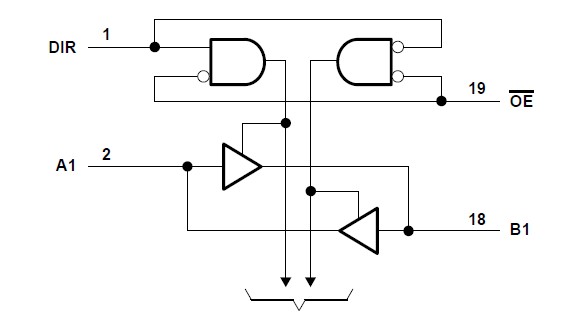

The 74ACT245DW is an octal bus transceiver. The 74ACT245DW is designed for asynchronous two-way communication between data buses. The control-function implementation minimizes external timing requirements. When the output-enable (OE) is low, the 74ACT245DW passes noninverted data from the A bus to the B bus or from the B bus to the A bus, depending upon the logic level at the direction-control (DIR) input. A high on OE disables the device so that the buses are effectively isolated. To ensure the high-impedance state during power up or power down, OE should be tied to VCC through a pullup resistor; the minimum value of the resistor is determined by the current-sinking capability of the driver.

Parametrics

74ACT245DW absolute maximum ratings: (1)Supply voltage range, VCC: –0.5 V to 7 V; (2)Input voltage range, VI: –0.5 V to VCC + 0.5 V; (3)Output voltage range, VO: –0.5 V to VCC + 0.5 V; (4)Input clamp current, IIK (VI < 0 or VI > VCC): ±20mA; (5)Output clamp current, IOK (VO < 0 or VO > VCC): ±20mA; (6)Continuous output current, IO (VO = 0 to VCC): ±50mA; (7)Continuous current through VCC or GND: ±200mA; (8)Package thermal impedance, θJA DB package: 70℃/W, DW package: 58℃/W, N package: 69℃/W, NS package: 60℃/W, PW package: 83℃/W; (9)Storage temperature range, Tstg: –65℃ to 150℃.

Features

74ACT245DW features: (1)4.5-V to 5.5-V VCC Operation; (2) Inputs Accept Voltages to 5.5 V; (3)Max tpd of 8 ns at 5 V; (4)Inputs Are TTL-Voltage Compatible.

Diagrams

|

74AC00 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||

|

74AC00MTC |

Fairchild Semiconductor |

Gates (AND / NAND / OR / NOR) Qd 2-Input NAND Gate |

Data Sheet |

|

|

||||||||||||

|

74AC00MTCX |

Fairchild Semiconductor |

Gates (AND / NAND / OR / NOR) Qd 2-Input NAND Gate |

Data Sheet |

|

|

||||||||||||

|

74AC00MTR |

|

IC GATE NAND QUAD 2INPUT 14-SOIC |

Data Sheet |

Negotiable |

|

||||||||||||

|

74AC00PC |

|

IC GATE NAND QUAD 2-INPUT 14-DIP |

Data Sheet |

Negotiable |

|

||||||||||||

|

74AC00SC |

Fairchild Semiconductor |

Gates (AND / NAND / OR / NOR) Qd 2-Input NAND Gate |

Data Sheet |

|

|

||||||||||||

(Hong Kong)

(Hong Kong)